<ド素人目線>PS5の内部構造?錯綜する噂と明らかになった点

9/21 更新

CPUは統合型L3キャッシュを採用している?

この話はPS5ローンチ後にRed Gaming Techの独自ソースにより公表されました。

内容としてはPS5のCPU基本設計はZen2に基づくもののL3キャッシュに関してはZen3と同じように統合型のL3キャッシュを採用してるとのことでした。

Zen2世代では1CCDに対して2CCX構成をとっており、L3キャッシュは各CCXのExcrusive Cacheとして存在。つまり別のCCX内のL3キャッシュにアクセスする場合はレイテンシが発生するためパフォーマンスに影響するとのことでした。

CCXの構成は初代Zenのころから1CCX=4コアになっており、CCXを2つ束ねた形で一つのダイに納める形で8コアCPUを実現しました。

Zen2でIO分離方式を採用してもこのCCX構成は基本的に受け継がれる形でした。

これがZen3からは改善され各CCXのL3キャッシュが統合化され実質的に1CCDに1CCX=8コアという形になりました。

話をPS5に戻します。

Red Gaming Techによれば

The L3 cache is unified like Zen 3, but it’s only 8MB according to what I am told. This information I am pretty confident in as two people have told me this,

つまり二人の匿名の開発者から話を聞いたそうです。

事前にPS5システムで統合型L3キャッシュ前提の特許図があったことからこの説を裏付けるものではないかと大いに期待されることとなります。(関連特許が見つけられませんでした。あくまで噂なんですかね)

そんな中で時は流れ、今年の二月ごろ有志によるPS5のダイ解析が行われたところ

A first quick and dirty die-shot of the PS5 APU (better SWIR image will follow). It looks like some Zen 2 FPU parts are missing. pic.twitter.com/PefXCxc3G1

Awesome work by Fritzchens again!

— Locuza (@Locuza_) 2020年11月8日

FPU and uCode position appears to be the same.

L1D$ looks very similar.

uOP$, L1I$, BTBs were moved a bit and look quite different.

L2$ appears nearly identical.

L3$ design has multiple changes.

A Zen3 core is quite a bit longer than a Z2 Core https://t.co/NVC1I9XlUW pic.twitter.com/G6TlsjQ2eg

— Fritzchens Fritz (@FritzchensFritz) 2021年2月14日

It busted this rumor.

— Locuza (@Locuza_) 2021年2月14日

There are two Zen2 CCX complexes as on AMD's Renoir with 8MiB L3$ per Complex.

No unified L3$ for all cores. pic.twitter.com/WZ6BZ4TRIp

どうやらL3キャッシュは統合化されてはいないらしく、CPUの配置もRenoirに近いところからZen2そのものに間違いないとは判明しました。

PS5に統合型キャッシュが採用されてるならZen3のように一体となったCCXデザインが採用されてなければおかしいからです。

PS5の場合は各CCXがそれぞれInfinity Fabric IOにつながるようなデザインなので直接、隣のCCXのL3キャッシュにアクセスすることは物理的にあり得ないという見解ですね。

PS5やRenoir世代のZen2の場合、別のCCXのL3キャッシュにアクセスする場合はIOを経由する形になるからレイテンシが発生する流れになるわけです。

ちなみにこれがZen3のレイアウト

Awesome work by Fritzchens again!

— Locuza (@Locuza_) 2020年11月8日

FPU and uCode position appears to be the same.

L1D$ looks very similar.

uOP$, L1I$, BTBs were moved a bit and look quite different.

L2$ appears nearly identical.

L3$ design has multiple changes.

A Zen3 core is quite a bit longer than a Z2 Core https://t.co/NVC1I9XlUW pic.twitter.com/G6TlsjQ2eg

しかし、この解析で思わぬことが判明しました...

SIMD部分に手を加えている?

. @Locuza_ (There is a higher res CCX shot on @FritzchensFritz's flickr now)

— Nemez (@GPUsAreMagic) 2021年2月15日

I have even more questions than before... (PS5 rescaled and slightly distorted to fit existing Zen 2 pic, but that shouldn't really skew it much) pic.twitter.com/Rf50qsM5GK

PS5のCPUがZen2そのものではなく、何かしらの手が加えられてるのではないかという話が浮上しましたそれが上のツイートです。

詳細を言うとSIMDユニットが半減してるのではないかという疑惑です。

写真のとおり、SIMDユニットのサイズがPC向けのZen2とPS5では異なります。

Zen2からSIMDユニットは256bitまで拡張されAVX命令をネイティブに実行できるようになっていますが、ゲームにおいてはあまり使われないことからSIEの方針によりオミットされたのではないかということです。(浮動小数点演算ではGPUのが速いですし、SIMDにわざわざ最適化しても正直微妙なケースが多いらしい)

しかし、後に改めて詳細な解析を行ったところ

So turns out it actually is all there (PS5 Zen FPU), just cut down a bit I guess (feature-wise) and the register file is halved.

— Nemez (@GPUsAreMagic) 2021年2月17日

One side (top) has a bit more stuff so I assume thats the side with the converter and maybe some of the standard crypto stuff left in the FMAD unit... pic.twitter.com/m2DNL7hYDZ

SIMDユニット自体はZen2と同じものを実装してるとのこと。

ではなぜ削除されたように見えたのかについては、レジスタファイルが減ってる可能性があるとのことです。

Well, @FritzchensFritz got hands on a PS5 again and did some awesome die shots!

— Locuza (@Locuza_) 2021年8月27日

Vanilla Zen2:https://t.co/9RLFbKGhpy

PS5 CPU Core:https://t.co/gC2xIHkmQD

The custom Zen2 CPU for Sony is only modified on the FPU side, digital logic and everything else looks identical.

1/x pic.twitter.com/hiUkOWVfLw

ZenからZen2、Zen3のFPレジスタはSIMD長に違いはあれど160個、固定の数値となっていますが、PS5の場合は120個に落としてる可能性が確認できたということです。

((9/21 追記

当初、レジスタファイル数の削除が確認されたと記述しましたが、続報があります。

レジスタファイル削除ではなく、設計最適化による縮小化の可能性が提示されました。

現時点では確定とも言えないで追記ということで対応させていただきます。

))

理由に関してはわかりませんが、すでに述べた通りゲーム用途で過剰なSIMD性能をCPUに求めるのは無意味であるということです。(実際のところは最適化が難しく、思うような性能が担保できないという点)

数は減ってるといえども個数自体は全体の1/4程度を削っただけでレジスタが枯渇しない限り、性能低下は少ないといえるかもしれません。

結果的にオミットされた分だけSIMDユニットを縮小させることができ、おそらく電力面で言えば意図的にSIMD処理を抑えることで省電力化を達成したのかもしれません。

SIMD処理における発熱はAVXクロックの名前で知られてる通り、専用クロックプロファイルを設定して発熱を抑えてることでも知られてます。

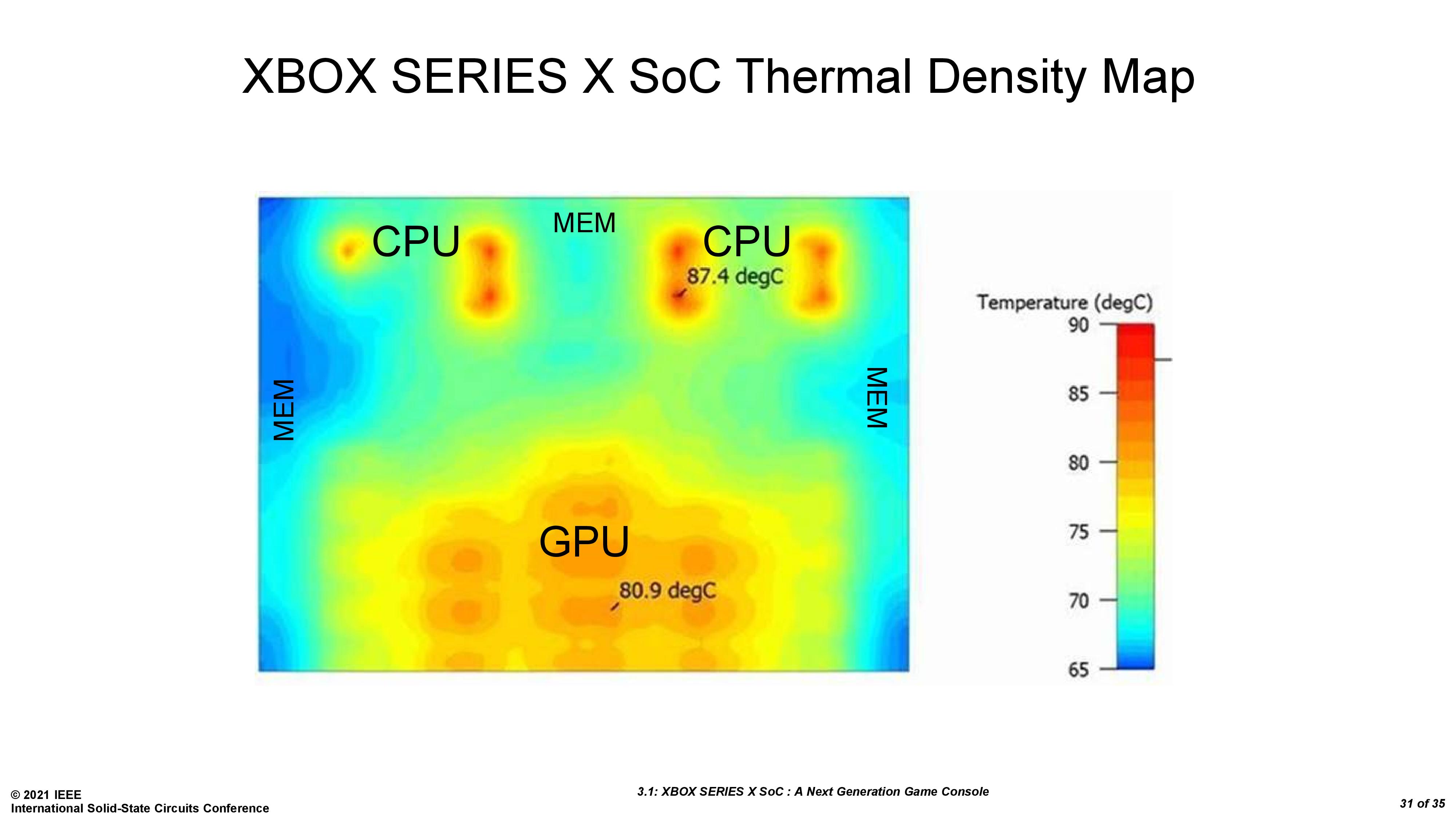

SIMDユニットの発熱に関しては、Xboxを有するライバルのMicrosoftもその点は認識しており、本体の熱設計に関してのプレゼンで紹介されてました。

Xbox Series X SoC: Power, Thermal, and Yield Tradeoffs

見ての通りGPUより、CPUのSIMDユニットが高発熱の傾向にあります。

SIEはこれを嫌がったためにこのような設計をしたのかもしれません。(面白いことにXbox SeiresはSとXともにフルのSIMDユニットを採用しておりPS5とはまた異なる選択をしました。)

終わりに

ここまでいろいろと書いてきましたが、実のところ情報をすべて有志の検証結果から引用しています。

SIEはPS5のアーキテクチャ詳細に関して、GDC2020の「The Road to PS5」 以降、

詳細を公にはしてません。

そのため公式の情報はかなり抽象的なものになっており、詳細なアーキテクチャに関しては謎に満ちています。(SIEの秘密主義はPS4Proのころから表れてますね...)

幸いSoCの解析が進み、ダイレイアウトからCPU、GPU、IOブロックの詳細が鮮明に映し出されました。

いろいろ物議をかもしそうなところもありますが、今回は扱いやすそうなCPUに限って取り上げてみました。

また、何かあれば記事に書き出そうと思います。

それでは、また。